基于Quartus的数字电子钟设计 实现计时、校时、闹钟、秒表及音频功能

数字电子钟是数字电路设计的经典应用之一,它结合了时序逻辑、组合逻辑以及用户交互功能。本项目基于Quartus II软件平台,设计并实现了一个多功能数字电子钟,具备计时、校时、闹钟、秒表和音频提示功能。以下将详细介绍电路设计思路、关键模块实现方法,并提供工程文件分享。

一、系统总体设计

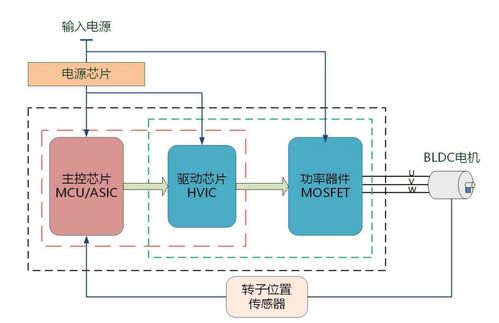

数字电子钟系统主要由以下模块组成:时钟源模块、计时模块、校时控制模块、闹钟模块、秒表模块和音频输出模块。系统采用FPGA或CPLD作为核心控制器,通过Quartus进行逻辑设计、仿真和下载。

二、各模块设计与实现

- 时钟源模块:使用晶振提供基准时钟信号,通过分频电路生成1Hz信号用于计时。在Quartus中,可通过计数器实现分频,例如将50MHz时钟分频至1Hz。

- 计时模块:采用BCD计数器实现时、分、秒的计数,并通过七段数码管显示。设计时需注意进位逻辑,例如秒计满60向分进位,分计满60向时进位,时计满24归零。

- 校时模块:通过按键输入实现时间和闹钟的调整。使用消抖电路处理按键信号,通过状态机控制校时模式(例如按一次键进入小时调整,再按进入分钟调整)。

- 闹钟模块:设置闹钟时间并存储,当计时时间与闹钟时间匹配时,触发音频输出。可通过寄存器存储闹钟值,并设计比较器进行时间匹配检测。

- 秒表模块:独立于主计时功能,实现启动、暂停、复位操作。使用计数器记录秒表时间,并通过控制逻辑管理状态切换。

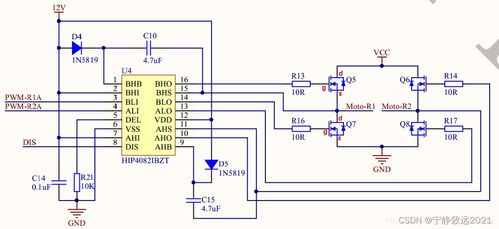

- 音频模块:当闹钟触发或秒表达到特定时间时,输出音频信号。可采用PWM(脉冲宽度调制)或简单方波驱动蜂鸣器,实现不同频率的提示音。

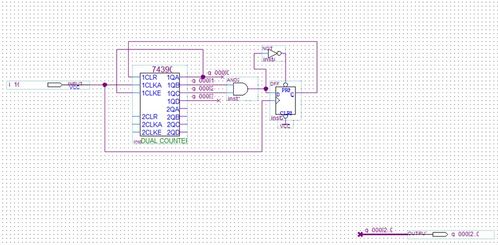

三、电路图设计与工程文件

在Quartus中,设计采用原理图输入方式,结合VHDL或Verilog代码实现复杂逻辑。关键电路包括:

- 分频器电路:用于生成1Hz和音频所需频率。

- BCD计数器和显示驱动:驱动数码管显示时间。

- 按键输入处理电路:包括消抖和状态控制。

- 音频生成电路:基于计数器的方波发生器。

工程文件包括:

- 顶层原理图文件(.bdf)

- VHDL/Verilog模块文件(.vhd或.v)

- 引脚分配文件(.qsf)

- 仿真波形文件(.vwf)用于功能验证

四、集成电路设计服务

对于更复杂的应用,可提供集成电路设计服务,包括:

- 定制化数字电子钟IP核设计

- 多时钟域管理优化

- 低功耗设计(适用于便携设备)

- 系统集成与测试支持

五、总结

本设计通过Quartus平台实现了功能丰富的数字电子钟,涵盖了从基础计时到高级交互功能。该方案注重模块化设计,便于扩展和修改。工程文件和电路图可供学习和二次开发,适合数字电路实验和嵌入式系统入门。未来可进一步添加温度显示、蓝牙控制等功能,提升实用性。

注:工程文件及详细电路图可通过联系作者获取,确保遵循开源协议用于教育和研究目的。

如若转载,请注明出处:http://www.xiangchebaitiao.com/product/37.html

更新时间:2026-04-16 01:35:03